728x90

반응형

사실상, 반도체 선단 공정(노광)은, 매년 두배씩 성능이 향상된다는 "무어의 법칙"이 깨진 지 오래입니다. 선단 공정의 허들이 높아지면서, 더 향상된 칩을 기대하는 수요에 맞추기 위해, 다양한 패키징 공정 기술이 개발되고 있습니다. 나에게 반도체의 미래를 이야기하라면, EUV, ALD, PACKGE를 말할 듯싶습니다.

수많은 제조공정(전공정)을 거친 반도체 칩은 마지막 절차인 테스트(후공정)를 통해 양품, 불량품을 선별하게 됩니다. 반도체 제조과정에서는 다양한 테스트가 이루어지는데요. 반도체 8대 공정 1편에서 3편까지는 반도체 제조 공정이었다면, EDS 공정과 패키징 공정은 테스트와 조립, 포장에 관한 공정입니다.

7. EDS공정

완전한 반도체로 태어나기 위한 첫 번째 공정입니다. EDS공정(Electrical Die Sorting)은 웨이퍼 위에 전자회로를 그리는 FAB 공정과 최종적인 제품의 형태를 갖추는 패키지 공정 사이에 진행됩니다. 즉 전기적 특성검사를 통해 개별 칩들이 원하는 품질 수준에 도달했는지를 확인하는 공정으로써 그 목적은 아래와 같습니다.

1) 웨이퍼 상태 반도체 칩의 양품/불량품 선별

2) 불량 칩 중 수선 가능한 칩의 양품화

3) FAB 공정 또는 설계에서 발견된 문제점의 수정

4) 불량 칩을 미리 선별해 이후 진행되는 패키징 공정 및 테스트 작업의 효율 향상

먼저, 전기적 특성검사를 통해 각각의 칩들이 원하는 품질 수준에 도달하는지 체크합니다. 그 후, 양품 가능 여부를 판단해, 수선(Repair) 가능한 칩은, 다시 양품으로 만들고, 불가능한 칩은 특정 표시(Inking)를 통해 불량으로 판정합니다.(수율 향상) 불량으로 판정된 칩은 이후 공정에서 제외되어 효율을 높일 수 있습니다.

EDS공정은 반도체의 수율을 높이기 위해 반드시 필요한 공정입니다. 수율은 웨이퍼 한 장에 설계된 최대 칩(Chip) 개수 대비 생산된 양품(Prime Good) 칩의 개수를 백분율로 계산한 것으로, 반도체의 생산성과 직결됩니다.

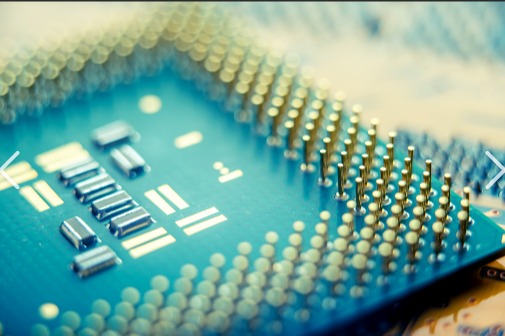

EDS공정은 프로브 카드(Probe Card)에 웨이퍼를 접촉시켜 진행됩니다. 프로브 카드에 있는 수많은 미세한 핀(Pin)이 웨이퍼와 접촉해 전기를 보내고 그 신호를 통해 불량 칩을 선별하게 됩니다.

728x90

# EDS공정의 4단계

EDS공정은 세분화된 여러 단계가 있지만, 크게 4단계로 나눌 수 있습니다.

1단계 – ET Test & WBI(Electrical Test & Wafer Burn In)

ET Test(Electrical Test)는 반도체 집적회로(IC) 동작에 필요한 개별소자들(트랜지스터, 저항, 캐패시터, 다이오드)에 대해 전기적 직류전압, 전류 특성의 파라미터를 테스트하여 동작 여부를 판별하는 과정입니다. 반도체 칩(Chip)으로 행하는 첫 테스트라고 볼 수 있습니다.

이어지는 WBI공정(Wafer Burn In)은 웨이퍼에 일정 온도의 열을 가한 다음 AC(교류)/DC(직류) 전압을 가해 제품의 결합, 약한 부분 등 잠재적인 불량 요인을 찾아냅니다. 제품의 신뢰성을 효과적으로 향상하는 공정입니다.

2단계 – Hot/Cold Test

Hot/Cold 공정에서는 전기적 신호를 통해 웨이퍼 상의 각각의 칩 중 불량품이 있는지 판정합니다. 수선 가능한 칩은 수선 공정에서 처리하도록 정보를 저장하는데요. 이때, 특정 온도에서 정상적으로 동작하는지 판별하기 위해 상온보다 높고 낮은 온도의 테스트가 병행됩니다.

3단계 – Repair / Final Test

Repair 공정은 EDS공정에서 가장 중요한 단계인데요.

Repair공정에서는 Hot/Cold 공정에서 수선 가능으로 판정된 칩들을 수선하고, 수선이 끝나면 Final Test 공정을 통해 수선이 제대로 이루어졌는지 재차 검증하여 양/불량을 최종 판단합니다.

4단계 – Inking

Inking 공정은 불량 칩에 특수 잉크를 찍어 육안으로도 불량을 식별할 수 있도록 만드는 공정을 의미합니다. Hot/Cold Test 공정에서 불량으로 판정된 칩, Final Test 공정에서 재검증 결과 불량으로 처리된 칩, 그리고 웨이퍼에서 완성되지 않은 반도체 칩(Dummy Die) 등을 구별하는데요. 과거의 Inking 공정은 불량 칩에 직접 잉크를 찍었으나 현재는 Data만으로 양/불량을 판별할 수 있도록 처리하고 있습니다. 이렇게 처리된 불량 칩은 조립 작업을 진행하지 않기 때문에 조립 및 검사 공정에서 사용되는 원부자재, 설비, 시간, 인원 등의 손실 절감 효과가 있습니다.

Inking공정을 마친 웨이퍼는 건조(Bake)된 후, QC(Quality Control) 검사를 거쳐 조립공정으로 옮겨지게 됩니다.

8. 패키징 공정(Packaging)

웨이퍼 완성 단계에서 이루어지는 테스트 ‘EDS 공정(Electrical Die Sorting)’을 마친 반도체들은, 마지막으로 완벽한, 반도체 제품으로 태어나기 위한 단계 ‘패키징(Packaging) 공정’을 거치게 됩니다.

#) 반도체를 외부환경으로부터 보호하고, 전기적으로 연결해주는 공정.

전공정을 통해 완성된 웨이퍼의 반도체 칩은 낱개로 하나하나 잘라내는데, 이렇게 잘린 칩을 베어칩(bare chip) 또는 다이(die)라고 합니다. 그러나 이 상태의 칩은 외부와 전기신호를 주고받을 수 없으며, 외부 충격에 의해 손상되기 쉬운데요. 반도체 칩, 즉 집적회로(IC)가 기판이나 전자기기에 장착되기 위해선 그에 맞는 포장이 필요합니다. 이와 같이 반도체 칩이 외부와 신호를 주고받을 수 있도록 길을 만들어주고 다양한 외부환경으로부터 안전하게 보호받는 형태로 만드는 과정을 ‘패키징(Packaging)’이라고 합니다.

패키징은 집적회로와 전자기기를 연결하고 고온, 고습, 화학약품, 진동/충격 등의 외부환경으로부터 회로를 보호하기 위한 공정입니다. 점차적으로 선단 공정의 한계성이 드러나면서, 최근 몇 년에 부각되고 있는 분야입니다.

#) 삼성 전자의 경쟁사인 TSMC에서 FO-WLP 패키징으로 애플의 마음을 사로잡은 것으로 유명합니다.

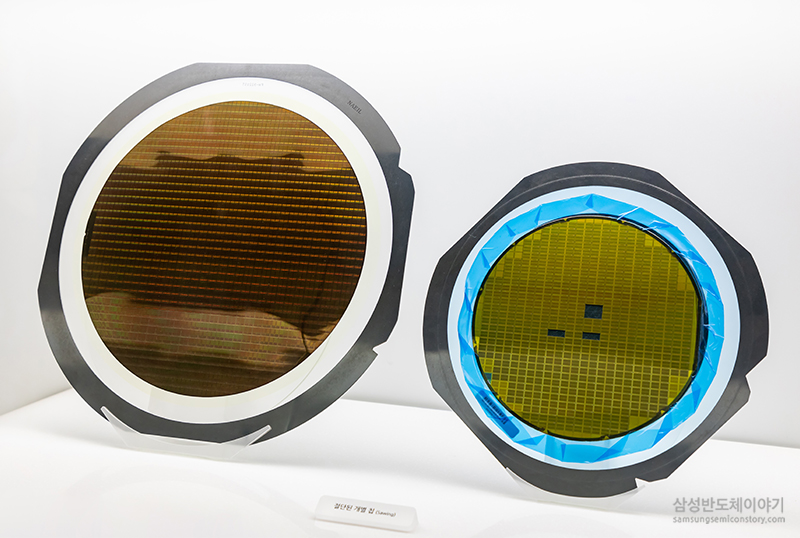

1) 웨이퍼 절단

# 개별 절단된 칩

먼저, 웨이퍼를 낱개의 칩으로 분리해야 합니다. 웨이퍼에는 수백 개의 칩이 촘촘히 배열되어 있고, 각 칩은 스크라이브 라인(Scribe Line)으로 구분되어있는데요. 이 스크라이브 라인을 따라 웨이퍼를 다이아몬드 톱이나 레이저 광선을 이용해 절단합니다. 웨이퍼 절단 작업은 웨이퍼를 톱질하고 잘라낸다는 의미에서 ‘웨이퍼 소잉(Wafer Sawing)’이나, ‘다이싱(Dicing)’이라 불립니다.

2) 칩 접착(Die attach)

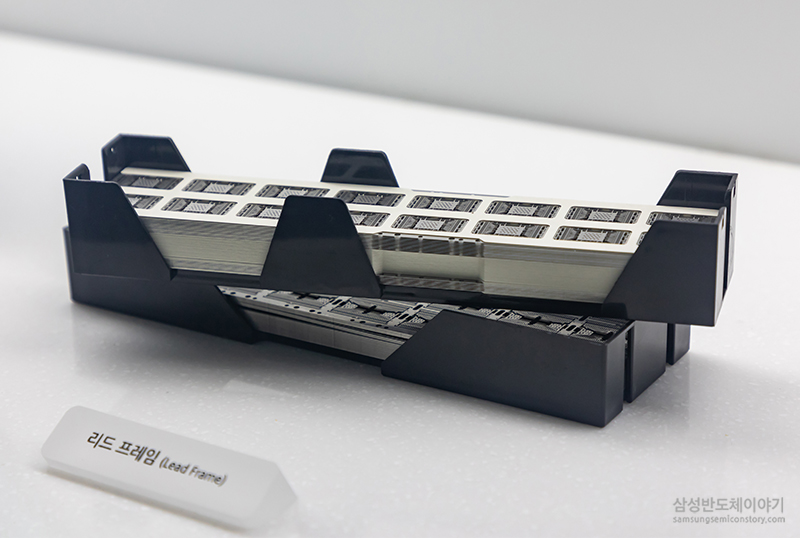

# 칩의 지지대 역할을 하는 리드프레임

절단된 칩들은 리드프레임(Lead Frame) 또는 PCB(Printed Circuit Board) 위에 옮겨집니다. 리드프레임은 반도체 칩과 외부 회로 간 전기신호를 전달하고, 외부 환경으로부터 칩을 보호, 지지해주는 골격 역할을 합니다.

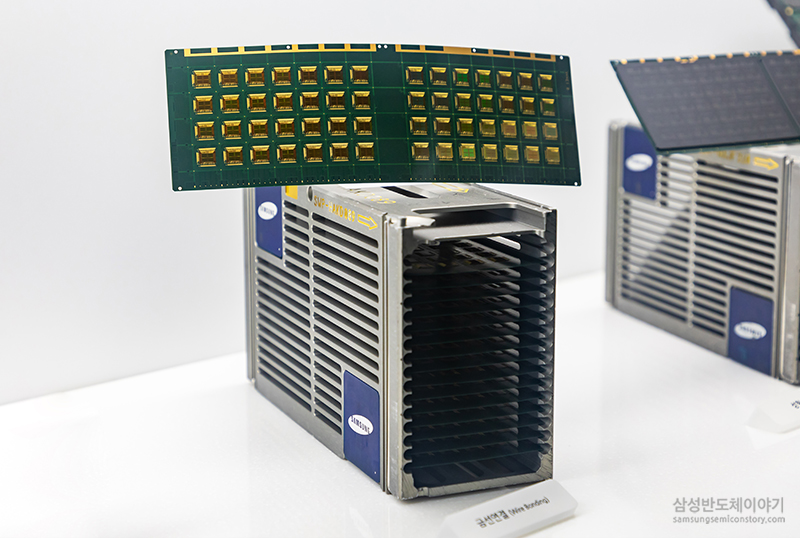

3) 금선 연결

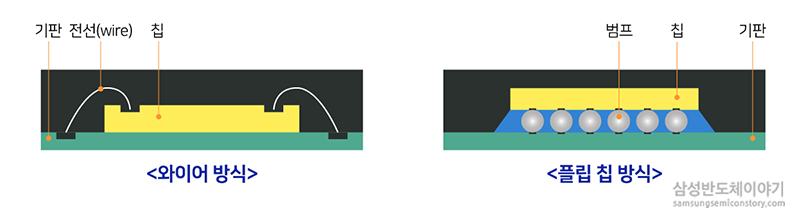

반도체의 전기적 특성을 위해 기판(PCB) 위에 올려진 반도체 칩의 접점과 기판의 접점을 가는 금선을 사용하여 연결하는 공정을 와이어 본딩(Wire Bonding)이라고 합니다.

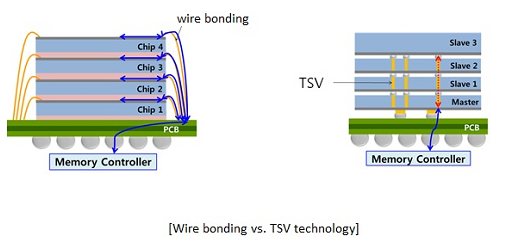

TSV(through silicon via, 실리콘 관통전극)은 와이어를 이용해 칩을 연결했던 적층 기술인 와이어 본딩(wire bonding)을 대체하는 기술로, 칩에 미세한 구멍(via)을 뚫어 상단 칩과 하단 칩을 전극으로 연결하는 패키징(packaging) 기술입니다. 이는 추가적인 공간을 요구하지 않아 패키지 크기를 소형화할 수 있고, 칩 간의 상호접속(interconnection) 길이를 감소시킬 수 있다는 점에서, 고집적도(high density)를 통한 전자부품의 소형화 및 빠른 신호전달, 고용량, 저전력에 유리합니다.

# 와이어 방식과 플립칩 방식 비교

전통적인 와이어 본딩 방식 외에 반도체의 속도를 향상하기 위해 칩의 회로와 기판을 직접 볼 형태의 범프(Bump, 돌기)로 연결하는 패키징 방식도 있는데요. 플립칩(Flip Chip) 패키징은 와이어 본딩보다 전기 저항이 작고 속도가 빠르며, 작은 폼팩터(Form Factor) 구현을 가능하게 합니다.

범프의 소재로는 주로 금(Au) 또는 솔더(Solder, 주석/납/은 화합물)가 사용됩니다.

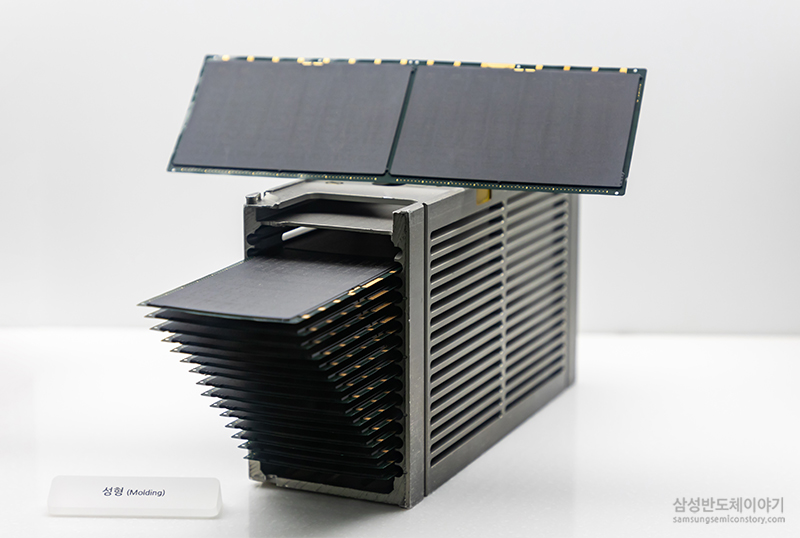

4) 성형(Molding) 공정

# 반도체 칩을 화학 수지로 밀봉하는 성형(Molding) 공정

금속 연결 공정까지 끝나면 열, 습기 등의 물리적인 환경으로부터 반도체 집적회로를 보호하고, 원하는 형태의 패키지로 만들기 위한 성형(Molding) 공정을 거칩니다. 금선 연결까지 끝난 반도체 칩을 화학 수지로 밀봉하는 공정을 거치면 우리가 흔히 보는 반도체가 됩니다.

* 완벽한 반도체 제품을 위한 최종 관문, 패키지 테스트(Package Test)

패키징 공정을 마친 반도체 칩. 완성된 반도체는 최종 테스트 과정을 거쳐 우리 삶의 다양한 곳에 쓰입니다.

패키징 공정이 완료되면 반도체 제품의 최종 불량유무를 선별하는 패키지 테스트(Package Test)를 시행합니다. 이 테스트는 완제품 형태를 갖춘 후에 검사를 진행하기 때문에 ‘파이널 테스트(Final Test)’라고도 하는데요. 패키지 테스트는 반도체를 검사장비(Tester)에 넣고 다양한 조건의 전압이나 전기신호, 온도, 습도 등을 가해 제품의 전기적 특성, 기능적 특성, 동작 속도 등을 측정합니다. 또한, 테스트 데이터를 분석해 제조공정이나 조립공정에 피드백함으로써 제품의 질을 개선하는 역할도 합니다.(차후, 수율 향상에 기여)

# 애플을 사로잡았던, TSMC의 FO-WLP 패키징에 대해 이야기하겠습니다.

설명에 앞서 개념 이해를 돕기 위해, 추가적인 설명을 하겠습니다.

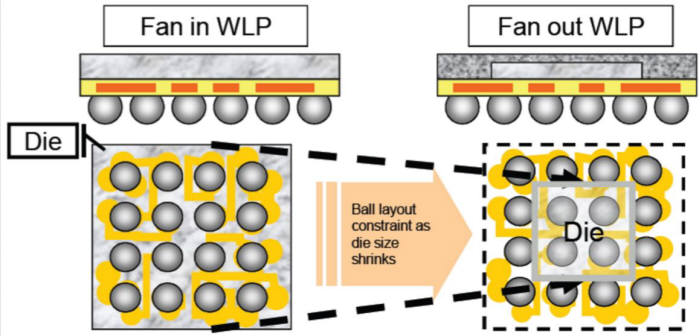

핵심적인 단어인 FO(Fan-Out)와 WLP(Wafer Level Package)에서, WLP는 말 그대로 웨이퍼 상태로 패키징 하는 방식을 이야기합니다.

FO(Fan-Out))라는 것은, 다이 사이즈보다 큰 면적에 볼(ball)이 있는 구조로, 이때 볼은 칩(Die)과 기판을 전기적인 기능을 할 수 있도록 연결해주는 역할을 합니다. 반대로, FI는 Fan-In의 약자로 칩(Die) 면적 안에 볼(ball)이 있는 모양입니다. 현재, 다이(칩)의 크기가 줄어들고 있는 상활에서 FI에서의 볼은, 칩의 크기에 맞추어 같이 작아져야 합니다. 일괄적인 볼의 레이아웃(Layout, 배치) 이 어렵다는 단점이 있습니다. 또한, FO는 FI에 비해 하나의 다이(칩) 당 볼의 수가 많아, 패턴의 효율성을 높일 수 있습니다.

여기서 의하 한 점이 있을 겁니다. WLP는 다 FI이 되어야 하는 것이 아니냐는 점입니다. 하지만, FI-WLP는 웨이퍼를 자르지 않고, 패키징 한 후, 다이싱(절단) 하는 반면, FO- WLP의 경우는, 칩들을 자른 후에, 공정 진행하므로, 웨이퍼 테스트에서 양품으로 판정된 칩들만, 캐리어에 배열하여 불량품까지 패키지 공정을 진행하지 않아도 됩니다.

- 원하는 대로 패키지 크기 조절 가능하여 기존 패키지 테스트 인프라 사용 가능

→ 이러한 이유로 최근에는 적용범위가 커지고 있습니다.

# 추가적으로, 삼성 전자의 FO-PLP패키징에 대해 설명하겠습니다.

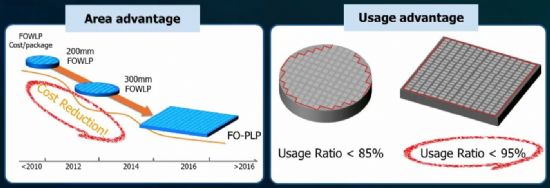

PLP(Panel Level packaging)은 칩과 기기를 잇는 선을 패널에 직접 심는 패키징 공정으로, WLP 공정 대비 한 번에 패키징 할 수 있는 칩의 수가, 20%정도 더 많아서 생산원가를 더 낮출 수 있습니다. WLP방식은 웨이퍼 모양과 같은 원형으로, 손실되는 부분이 있는 반면, 사각의 패널에 칩을 배치하면, 활용 못하고 손실되는 부분이 현저히 줄어듭니다. 하지만, 기존의 웨이퍼 공정 장비를 이용할 수 없어, 패널 공정이 가능 한 새 장비를 새로 개발해야 하고, 최소 패턴 형성 능력이 더 좋지 않습니다. 요약하자면, WLP 공정 대비 PLP가 앞선 기술로 평가받지만, 장비 개발과 패턴 형성 능력의 향상, 특히, 재료 간의 열팽창 계수의 차이로 휨 현상이 발생 등 개선될 요소들이 많은 것 같습니다. 삼성전자는 TSMC와의 파운드리 경쟁에서 앞서 나가기 위해 FO-PLP 패키징 기술을 내세웠습니다. (최근 발매하는 칩들은 FO-PLP를 활용하여 생산하는 것으로 알려졌습니다)

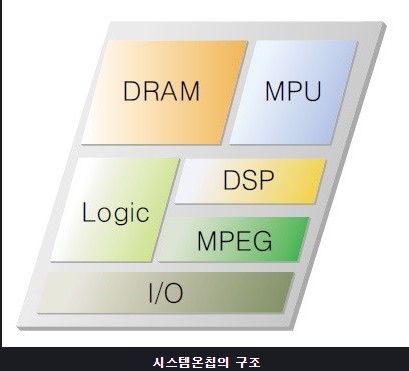

# PCB 기판의 쇼티지(Shortage)에 대하여

불과 얼마전 까지 패키징의 흐름은, PCB 기판을 사용하지 않는, TSMC의 FO-WLP 패키징(2015년)이 나온 이후, PCB 기판 업체들은 향후, 수요가 줄어들 것이라 예상하여, 시설 투자를 하지 않았습니다. 고성능의 AI용 칩들과 SOC(System On Chip)의 발열 문제로 다시 PCB 기판, 정확하게는 플립칩 BGA(Flip chip BGA) 기판을 필요로 하게 됐습니다. 여기서, 플립칩 BGA는 앞에 이야기한 플립칩 공정을 할 때의 기판을 이야기합니다 결국, 심각한 공급 부족(Shortage)으로, 현재의 칩 메이커(Chip maker)들이 선수금을 주고, 기판을 사 오고 있습니다. 이는, 기판을 만드는 재료 및 소재의 공급과 생산 장비(일본 기업) 부품이 원활하게 이루어지지 못한 매크로적인(중국 봉쇄, 러우 전쟁) 영향으로 더욱 증폭되고 있습니다. 새로운 공장을 짓고, 가동 시까지 1~2년의 시간이 소요되기에 단시간 내에 해결될 문제는 아닌 듯합니다.

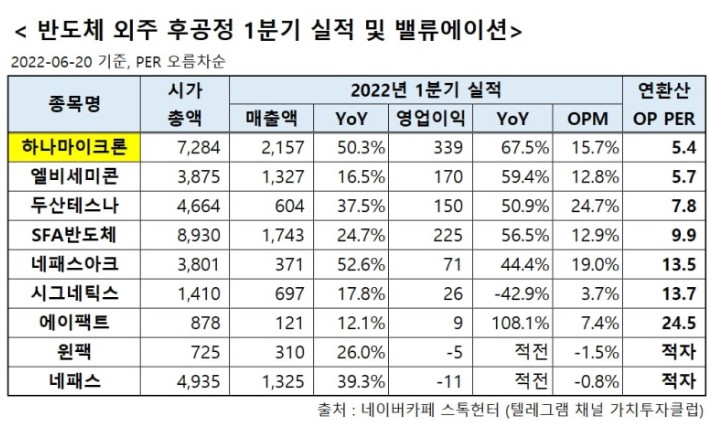

# 그럼 관련 기업에 대해 알아보도록 하겠습니다.

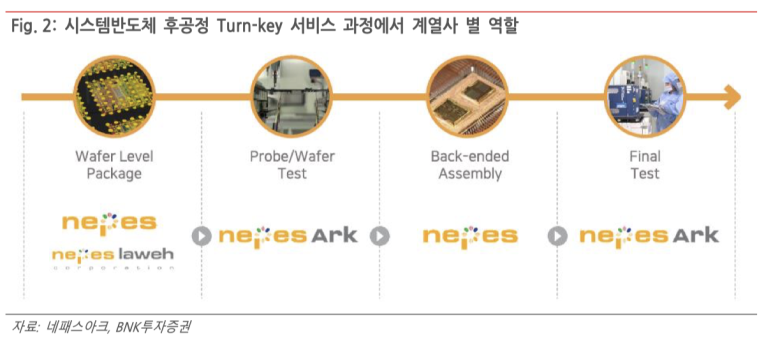

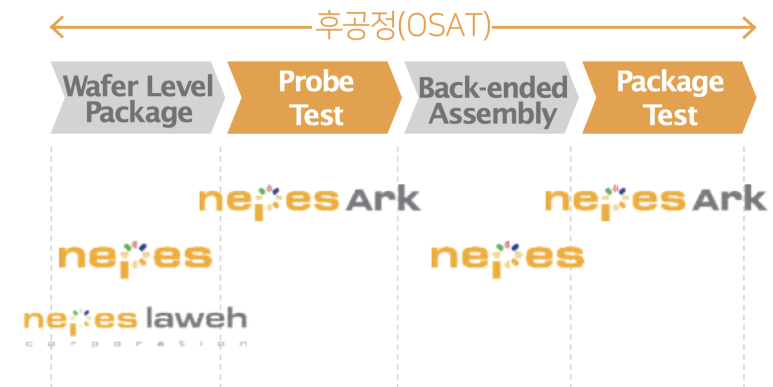

1. 네패스 아크

FO-WLP와 FO-PLP기술을 보유한 국내 유일의 기업입니다. 2019년 네패스에서 물적 분할하여, 20년 코스닥에 상장하였다. 삼성전자, NXP, 퀠컴등의 고객사를 확보하고 있으며, Package & Test 물량에 대해 Turn-key 계약방식으로 납품하고 있다.

다른 후공정(OSAT) 업체들과는 달리, 레거시 공정은 하지 않고, FOWLP와 FOPLP 등의 하이레벨 패키징 사업만을 영위하고 있다.

@ 종속 회사별 사업

네패스 : FIWLP, 네패스라웨 : FOWLP, FOPLP, 네패스 하임 : FOWLP, 네패스 아크: 테스트

네패스 아크가 각 연결 회사의 패키징 물량을 받아 최종 테스트 후 납품함.

2. 에스에프에이(SFA)

후공정(OSAT)의 플립칩 공정의 핵심기술 보유하고 있으며, 반도체 패키지의 고집적화 및 경박단소화 됨에 따라 플립칩을 기반으로 하는 패키징 시장이 꾸준히 상승 중이다.

3. 하나 마이크론

Flip Chip, Wafer Level Package(WLP), Multichip package(MCP)를 포함하는 다양한 패키지 군을 생산하고 있다.

# 우리나라 패키징의 3대 기업을 네패스, SFA반도체, 하나 마이크론이라 칭한다.

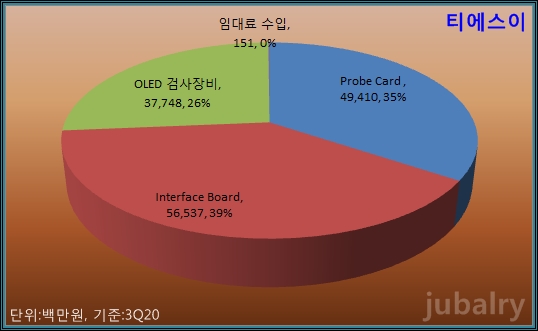

4. 티에스이(TSE)

반도체 및 디스플레이 검사장비 전문 기업으로써, 반도체 제조공정 중 전공정(Fabrication)이 완료된 웨이퍼(Wafer) 상태에서의 Test를 위한 핵심부품인 Probe Card, 후공정의 최종 검사 단계에서의 핵심 역할을 하는 Interface Board, LED의 전기적/광학적 특성을 검사하기 위한 Total Test Solution, OLED Tester, 반도체 IC Test Socket을 생산 및 판매하고 있습니다.

동사의 사업 중 Probe Card와 Interface Board, Test Socket은 반도체 산업에 속해 있으며, OLED/LED 검사장비는 디스플레이 산업에 속해 있습니다.

티에스이는 주로 Nand Flash 메모리 검사용 Probe Card를 생산하여 국내 삼성전자와 하이닉스에 공급하고 있습니다. 최근 Nand Flash는 스마트 디바이스와 SSD의 수요 증가로 인하여 DRAM 시장을 넘어서는 시장으로 성장하고 있으며, 이에 따라 제조사들의 공격적인 설비 확장이 지속적으로 이루어지고 있습니다.

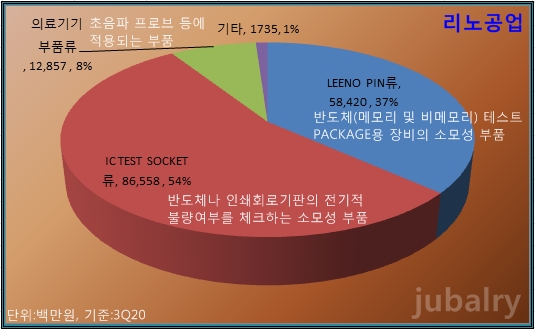

5. 리노공업

전량 수입에 의존하던 검사용 PROBE(SPRING CONTACT PROBE:LEENO PIN)와 반도체 검사용 소켓(IC TEST SOCKET)을 자체 브랜드로 개발하여 제조 및 판매하는 사업과 초음파 진단기 등에 적용되는 의료기기 부품을 제조 및 판매하는 사업 등을 영위하고 있습니다.

동사 제품은 40년 이상의 제품 생산 경험을 바탕으로 다품종, 주문생산이 가능하며, 다양한 반도체 공정 업체 및 전기전자 업체에서 사용되고 있습니다. 특히, LEENO PIN과 IC TEST SOCKET은 응용범위가 넓어 IDM 종합 반도체, Fabless, Foundry, Packaging & Test, 전기전자업 등 여러 사업분야에서 매출이 발생하고 있습니다.

동사는 반도체 및 전기전자업체 등 고객의 주문에 따라 제품을 설계하고 제작하므로 계절 변화에 따른 비수기, 성수기의 매출금액의 변동이 작으며, 안정적인 매출 성장을 이어가고 있습니다. 그러나, 경기하강의 시점에 관련 매출처의 급격한 투자규모 축소 및 수주의 하락으로 매출의 축소가 발생할 수 있습니다.

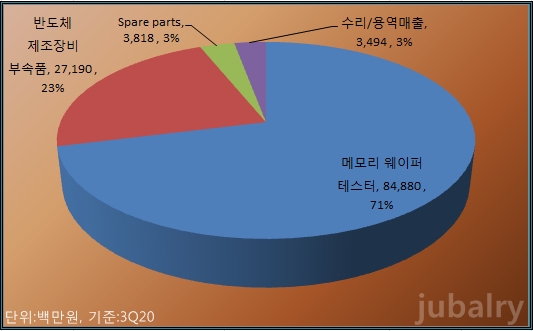

6. 와이아이케이

연결기업은 반도체 제조공정 중 EDS 테스트 공정에서 필요로 하는 반도체 검사 장비를 제작 및 판매하는 사업과 웨이퍼를 직접 컨택하여 테스트하는 프로브 카드에 사용되는 다층 세라믹 기판 제조 및 판매사업을 영위하고 있습니다.

반도체 핵심 재료인 웨이퍼의 검사기능을 수행하는 프로브 카드는 반도체 생산에 꼭 필요한 장비로 전자기기 및 시스템 산업 경기에 직접적인 영향을 받습니다. 특히, 웨이퍼 생산에 소모품으로 적용되어 반도체의 생산량에 따라 시장규모에 직접적인 영향을 받으며, 반도체의 생산공정의 기술변화의 속도에 따라 수요가 더 증가하기도 합니다. 반도체의 최종 수요처인 전자제품의 성능 및 기능의 다양화 및 태블릿 PC, 스마트폰 등 신규 애플리케이션 시장의 확대 등으로 전방산업의 약진이 예상되는 바 이에 따라 프로브 카드의 수요도 지속적으로 증가할 것으로 예상됩니다.

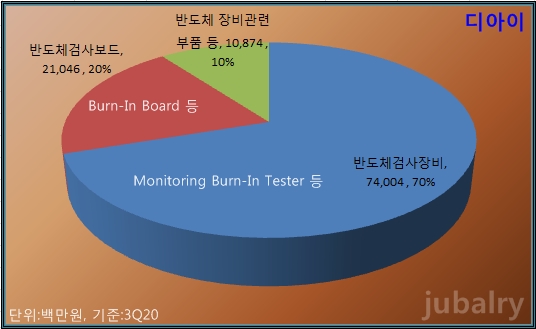

7. 디아이(D.I)

반도체 검사장비 제조 및 판매 등의 반도체 장비 사업부문, 전자파 차폐체(EMC) 등을 제조하는 전자부품 사업부문, 수(水) 처리 관련 환경사업 부문, 음향ㆍ영상기기 사업부문으로 구성되어 있습니다.

동사의 주력 제품인 번인 테스터와 번인 보드는 웨이퍼 상태 또는 패키징 된 칩에 전기적 신호와 고온/저온에 의한 스트레스 테스트 공정을 수행함으로써 반도체 기능의 내구성 및 신뢰성을 검증하는 반도체 검사장비입니다.

# 사실상 현재의 반도체 칩들은 선단 공정의 한계에 다다르면서, 패키징 기술이 부각되고, 발전되고 있습니다. 새로운 기술들이 계속해서 경쟁적으로 나오고 있기에 관심을 가지고, 지속적으로 지켜봐야 할 듯싶습니다.

https://https://youtu.be/bwMyGrXk-YU

728x90

반응형

'반도체, 삼성전자' 카테고리의 다른 글

| 삼성전자와 TSMC의 3나노 GAA의 비밀 (0) | 2022.12.18 |

|---|---|

| 삼성 전자의 결단, 겨울의 반도체, 불안한 TSMC (0) | 2022.12.13 |

| 반도체 8대공정 3편(5.증착 및 이온 주입 6.배선 공정) (0) | 2022.12.10 |

| 반도체 8대공정 2편(4. 식각 공정) (0) | 2022.12.09 |

| 반도체 8대공정 1편(1.웨이퍼 제조 2.산화 공정 3.포토 공정) (0) | 2022.12.08 |

댓글