오늘은 국내 패키징 업체 중에 주목해 봐야 할 기업을 소개해 보겠습니다.

반도체 8대 공정에 대해 이해가 어느 정도 있으신 분이 아니시라도 이해하실 수 있게 관련 내용에 대해 정리해 보았습니다. FST에 E-SOL이라는 든든한 자회사가 있다면, 네패스에는 네패스라웨는 국내 유일의 FOPLP(Fan-Out Pannal Level Packaging) 기술을 가지고 있는 자회사가 있습니다. 오늘도 사업보고서를 중심으로 네패스에 대해 알아보고 네패스 아크에 대해서도 이야기하고 주담통화로 마무리 짓도록 하겠습니다.

기업을 분석하기에 앞서 기본적인 패키징에 대해 짚고 가겠습니다.

패키징공정은 반도체를 완벽한 제품으로 만들기 위한 마지막 공정입니다. 반도체를 외부 환경으로 부터 보호할 뿐 아니라 내부의 열을 방출하고 전기적으로 연결해 주는 공정입니다. 즉, 집접회로와 전자기기를 연결하고 고온, 고습, 화학약품, 진동 및 충격등에 회로를 보호하기 위한 공정으로 칩의 미세화의 속도가 한계에 봉착하면서 최근 몇 년 부각되고 있는 분야입니다. 파운드리 최강자 TSMC는 당시 패키징 신기술이었던 FOWLP(Fan-out Wafer Level Package)을 이용하여 애플의 물량을 두고 삼성전자의 경쟁을 뿌리칠 수 있었습니다. TSMC가 FOWLP로 애플의 선택을 받기 전에는 패키징 공정은 전공정, 선단 공정보다 부각되지 못하는 취급을 받는 공정이었습니다.

[패킹징 공정 Process]

1. 웨이퍼 연마 및 절단

- 웨이퍼의 칩들은 수백 개의 스크라이브 라인(Scribe Line)에 따라 구분되어 있습니다. 이 스크라이브 라인을 따라 다이아몬드 톱이나 레이저 광선을 이용하여 절단하는 과정입니다. 이 공정을 다이싱(Dicing), 소싱(Sawing)이라 부릅니다.

2. 칩을 접착(Die attach)

- 칩을 지지해 주는 리드프레임(Lead Frame) 또는 PCB(Printed Circuit Board)로 옮겨집니다. 칩과 외부 회로 간 전기신호를 전달하고 외부 환경으로 부터 칩을 보호해 주는 골격 역할을 합니다.

3. 금선 연결

- 전통적인 와이어 본딩 방식과 와이어 본딩(Wire bonding) 방식의 단점을 극복하기 위해, 최근 주로 사용되는 범프를 이용한 플리칩 방식(Flip-Chip bonding)

와이어 본딩은 외곽으로 와이어를 이용하여 본딩 하는 반면, 플립칩 본딩은 범프를 이용하여 연결하는 방식으로 개별 칩마다의 활용 부피가 줄어들고 연결 속도가 빠르다는 장점이 있습니다. 칩을 건물이라 할 때 외부 계단이 와이어 본딩 방식이라면 범퍼는 엘리베이터, 플립칩 방식은 엘리베이터를 이용하여 층을 움직인다 할 수 있습니다. 우리가 계단을 이용하여 건물을 올라가는 것은 건물 외부의 별도의 공간을 활용하여 계단을 만들어 실제 활용할 수 있는 건물의 부피를 줄어들게 만들고 계단으로 오르는 것이 엘리베이터를 이용하는 것에 비해 느리고 힘이 들다고 이해하시면 됩니다.

그러나, 플립칩(Flip Chip)이라는 엘리베이터는 딱 한 층만 이동할 수 있는 엘리베이터로 적층 되어 있는 고층에는 이용할 수가 없습니다. 그래서 고층 엘리베이터인 TSV(Through Silicon Via, 실리콘 관통전극) 본딩 방식과 커플로 많이 쓰입니다. 위의 그림처럼 TSV는 칩에 미세한 구멍을 뚫어 상단과 하단의 칩을 전극으로 연결하는 패키징 기술입니다.

4. 성형 공정

- 열, 습기등의 물리적인 환경으로 반도체 칩을 보호하고 원하는 형태로 만들기 위해 화학 수지로 밀봉하는 공정을 거치면 우리가 흔히 보는 반도체의 모습이 됩니다.

5. 패키지 테스트(Package Test)

- 패키징 공정을 마친 반도체 칩은 최종 테스트를 거쳐 우리 삶의 다양한 영역에 쓰이게 됩니다. 이 공정은 최종 불량유무를 선별하는 단계로 패키징 테스트 검사 장비인 Tester에 넣고 다양한 조건의 전압, 전기신호, 온도, 습도 등을 가해 제품의 전기적, 기능적, 동작 속도 등을 확인하게 됩니다. 이 테스트는 완제품의 형태로 검사가 진행되기에 파이널 테스트(Final Test)로 불리기도 합니다. 이러한 파이널 테스트는 관련 데이터를 분석하여 제조공정 또는 조립공정을 피드백함으로써 제품의 질을 개선시키는 중요한 역할을 합니다. 이렇듯 차후 수율 향상에 영향을 줍니다.

여기서 애플의 마음을 사로잡았던 TSMC의 FOWLP와 삼성이 TSMC를 견제하여 만든 최신 패키징 기술인 FOPLP에 대해 알아보도록 하겠습니다.

1) WLP와 PLP의 차이

- 웨이퍼에 잘라진 칩 다이를 다시 둥근 모양의 웨이퍼에 배열하는 WLP(Wafer Level Package)와는 달리 네모 모양의 패널을 활용하여 패키징 하는 PLP(Panel Level Package)은 네모난 칩이 둥근 웨이퍼 모양에 칩을 접착하는 WLP가 전체 면적의 최대 85%를 활용할 수 있는 것에 반해, 별도의 네모난 패널(panel)을 활용하면 최대 95%를 활용할 수 있게됩니다. 삼성전자에서 개발하여 확장하고 있는 차세대 패키징 기술입니다. WLP에 비해 PLP는 한 번에 패키징 할 수 있는 칩의 개수가 10~20% 정도 더 많아져서 원가 절감(Cost Reduction)할 수 있다는 장점이 있습니다. 하지만 기존의 웨이퍼 공정 장비를 이용할 수 없어, 패널(Panel) 공정이 가능한 새 장비를 개발해야 하고 최소 패턴 형성 능력이 WLP대비 좋지 않다는 보완점을 가지고 있습니다. 업계에서 WLP대비 PLP가 앞선 기술로 평가되고 있지만, 새로운 장비 개발과 재료 간의 열팽창 계수의 차이로 휨 현상 발생등의 해결해야 할 요소가 아직 남아있습니다. 삼성전자는 TSMC와의 파운드리 경쟁에서 세계최초로 도입한 선단 공정 GAA뿐 아니라 패키징 공정에서도 FOPLP공정을 내세워 기술적 주도권을 가지려 하고 있습니다.

2) FI과 FO의 차이

- FO(Fan-Out))라는 것은, 다이 사이즈보다 큰 면적에 볼(ball)이 있는 구조로, 이때 볼은 칩(Die)과 기판을 전기적인 기능을 할 수 있도록 연결해 주는 역할을 합니다.(위 와이어 본딩과 플립칩 방식 비교 그림 참조) 반대로, FI는 Fan-In의 약자로 칩(Die) 면적 안에 볼(ball)이 있는 모양입니다. 현재, 반도체 미세화에 따른 다이(칩)의 크기가 줄어들고 있는 상활에서 FI에서의 볼은, 칩의 크기에 맞추어 같이 작아져야 합니다. 그렇기에 일괄적인 볼의 레이아웃(Layout, 배치) 이 어렵다는 단점이 있습니다. 또한, FO는 FI에 비해 하나의 다이(칩) 당 볼의 수가 많아, 패턴의 효율성(전기적 이동 속도 등)을 높일 수 있어 최근에 많이 활용되고 있습니다. 기존의 방식 FIWLP공정은 웨이퍼를 자르 지지 않고 패키징 후 절단하는 방식이었습니다. 그러나 이 방식은 양품이 아닌 불량칩까지도 통째로 패키징 해야 하는 문제점이 있었습니다. 이러한 문제점을 해결하기 위한 공정이 TSMC에서 개발한 FOWLP입니다. 웨이퍼를 패키징 후 다이싱(절단)하는 것이 아닌, 절단 후 양품만을 다시 배열하여 패키징 하는 방식으로 FIWLP대비 원가 절감이 가능합니다. 또한 FO이기 때문에 칩 면적당 Ball의 개수가 많아 패턴의 효율성이 좋아 최근에 가장 많이 쓰이는 방식이 FOWLP입니다.

우리나라 3대 패키징 기업으로는 네페스(nepes), 에스에프에이(SFA), 하나 마이크론이 있습니다. 그중 SFA는 최근 패키징 공정의 기본이 되는 Flip Chip공정의 핵심 기술을 보유하고 있으며, 하나 마이크론은 Flip Chip, WLP를 비롯한 MCP(Multichip package)를 포함하는 다양한 패키지 군을 생산하고 있습니다.

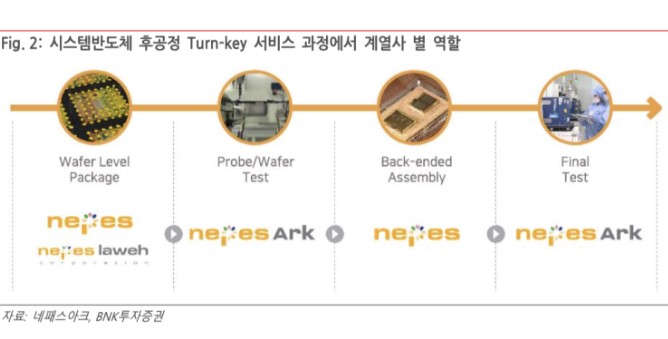

오늘 이야기할 네패스와 네패스의 자회사들은 Turn-key 방식으로 Package와 Test 물량을 납품하고 있습니다. 여기서 Turn-key는 일괄수주 계약이라 하며, 식당에서 음료부터 매인, 사이드 메뉴까지 총괄하여 제공되는 코스요리라 할 수 있습니다. 더욱이 네패스의 자회사 네패스라웨의 PLP관련 기술은 국내 유일의 기업입니다.

1. 개요

당사는 첨단 후공정 파운드리 사업과 반도체 및 디스플레이 제조에 사용되는 전자재료사업으로 구분되어 있습니다. 반도체 사업은 사업화에 성공한 플립칩(Flip Chip) Bumping 기술을 확보하여 스마트폰, 웨어러블 디바이스, 자동차 등 다양한 chip-set을 위한 WLP(Wafer Level Package), FOWLP 및 FO(FI) PLP 기술로 국내외에서 확고한 입지를 구출하고 있으며, 전자재료 사업은 현상액(Developer), 식각액(Etchant), PR(Photoresist), 세정제(cleaner)등의 소재 산업에 집중하고 있습니다.

최근 반도체 사업에 있어서 시스템반도체의 중요성이 부각되고 있으며, 시스템반도체 시장은 메모리 시장 대비 그 규모가 3배 이상의 거대한 시장입니다.(메모리 2.5 : 7.5 시스템) 현재, IT Application 시장을 주도하는 제품은 모바일에 기반을 둔 스마트 디바이스들이며 이를 구성하는 대부분의 부품은 시스템 반도체입니다. 당사의 첨단 후공정(OSAT) 사업은 파운드리 시스템반도체 Supply Chain의 핵심 공정이며, 국내뿐만 아닌 글로벌 수준의 기술을 선도하고 있습니다.

전자재료는 케미컬 시장의 특수성에 기인하여 변동성이 낮으며, 기능설 케미컬이 매출에 기여하기 시작하였습니다. 특히 전자재료 사업부문은 높은 국내 시장 점유율과 그동안의 기술 노하우를 바탕으로 수입에 의존하던 케미컬을 국산화하였으며, 내재화를 통한 신뢰성 검증을 통한 주요 고객대상 신규 매출을 기대하고 있습니다.

2 차전지용 부품을 국산화하여 ESS, EV용 배터리에 적용하여 급성장하는 에너지 분야로 영역을 확대하고 있습니다.

22년 3분기 전체 매출액은 4,469억 원이며, 반도체 부문 매출은 3,516억, 전자재료 412억, 2차 전지부문 541억입니다.

2. 판매경로

3. 판매 전략

1) 반도체 사업

- 주도적인 기술개발과 차별화된 연구를 바탕으로 한 안정적인 점유율(Maket Share) 확보

- global Marketing을 위한 고객 서비스 강화

2) 전자재료 사업

- Developer(현상액) 중심으로 이루어진 매출 구조를 신규 케미컬의 출시에 맞추어 고객 밀착영업 강화

- 기술영업 인원 보강 및 반도체 및 TFT-LCD 업체의 라인 증설 및 신규 참여사에 대한 선점영업과 해외지사를 거점으로 한 국제적 네트워크 형성 및 직수출 추진

4. 연구개발

1) 연구개발 비용

연구개발 비중이 높은 것으로 보아 성장을 위한 기술개발에 힘쓰고 있는 것으로 보입니다.

2) 연구개발 실적

-최근 3년간 연구 실적

5. 현황

1) 시장의 특성

반도체 사업분야인 시스템 반도체 분야의 고객은 삼성전자, DB하이텍 등으로 국내 LCD구동의 Bumping 기술을 최초로 Turn-Key 방식으로 국산화하여 장기 공급계약 체결을 하여 안정적 고객 및 공급처를 확보한 상황입니다. 2012년부터 글로벌 주요 비메모리 디자인하우스의 반도체 업체와 파트너십을 맺고 자사의 WLP(Wafer Level Packaging), FOWLP(Fan-out WLP) 기술을 공급하고 있습니다. 전자재료 사업분야는 대부분 반도체 완제품이 수출되어 원재료 구매는 내국신용장에 의한 로컬 수출로 이루어집니다. 반도체 및 LCD Maker의 생산공정은 연속적이고, 생산성 향상을 고려해야 하기에 선정된 재료에 한하여 거래처 변경이 용이하지 않아 지속적으로 안정적인 수요를 기대할 수 있습니다. 더불어 스마트폰용 전력관리 반도체 부문은 점차 시장점유율이 확대될 것으로 생각됩니다. 또한, 시스템 반도체 산업은 자체 Device의 가격 경쟁력을 확보하고, 안정적인 수급을 위하여 국산화 중에 있으며, 자체 기술력을 바탕으로 고객사와 협력을 통한 지속적인 제품개발을 추진하고 있습니다.

2) 신규사업 내용 및 전망

글로벌 시스템반도체 기술의 로드맵은 당사가 보유한 엔드팹 공정 기술 중심으로 빠르게 이동하고 있습니다. 또한 시스템 반도체의 주요 제조 체인이 대만에서 한국(삼성전자)으로 이원화되는 움직임을 보이고 있습니다. 그 관점에서 네패스는 글로벌 Top-tier 고객들과 협업하여 세계시장을 이끌어갈 첨단 기술 및 생산능력을 확장해 나가고 있습니다. 당사는 FOWLP관련 원천기술과 공정 혁신 기술을 활용하여 첨단 혁신 생산설비인 FOPLP를 구출하였으며 이를 통해 시스템 반도체의 핵심 밸류체인으로 성장해 나갈 전망입니다. 여기서 엔드팹은 생산라인에서 병목 현상이 생기는 지점의 처리능력을 이원화하여 강화함으로써 전체적인 생산 효율성을 높이는 것을 의미합니다.

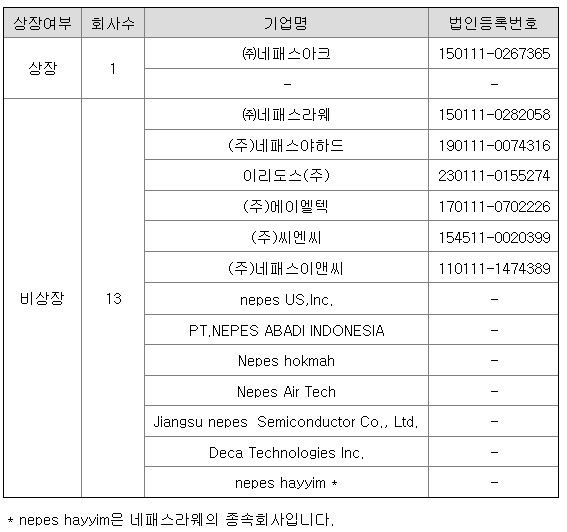

6. 자회사 현황

1) 주요 자회사

- 네패스아크

당사는 반도체 후공정 테스트 설루션을 제공합니다. 주요 제품군으로는 전력반도체(PMIC, Power Management IC), 디스플레이 구동칩(DDI, Display Drive IC), SoC(System on Chip) 및 기타 AP(Application Processor), RF(주파수, Radio Frequency) 및 5G 모뎀 chip 등이 있으며 2021년 하반기부터 네패스라웨의 FOPLP(Fan-out Panel Level Package) 제품의 테스트가 시작됐으며, 이미지센서(CIS, Cmos Image Sensor)의 진입을 준비 중입니다. 현재 631억 규모의 신규 시설 투자가 21년~22년 기간 동안 진행되고 있어 향후 매출 증가가 기대되고 있습니다. 이병구 대표이사(전 LG반도체)와 이창우 대표이사(전 네패스 상무)를 비롯한 주요 경영진이 네패스와 구 LG반도체의 인력입니다. 네패스 자회사 중 유일의 상장사입니다.

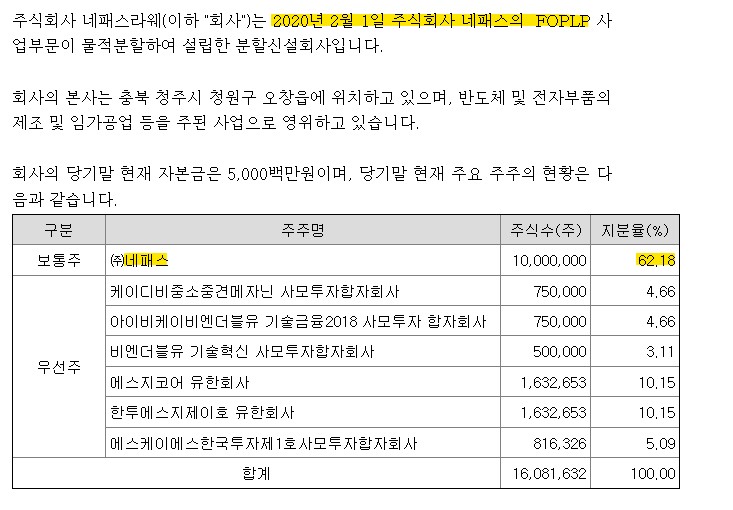

- 네패스라웨

- 네패스야하드

터치 스크린 패널 제조를 영위하는 자회사

- 네패스이앤씨

부동산 임대업과 건축 및 토목 공사를 영위하는 자회사

- 이리도스

LCD제품 관련 안료분산액(color paste)을 영위하는 자회사로 대표이사는 로드리고 엘리존드와 이병구입니다. Solvay S.A가 지분 49.34%, 네패스가 49.34%인 합작회사입니다.

7. 주담통화

1. 자회사 네패스라웨의 경우 삼성전자향 전담 FOPLP 만드는 회사로 보이는데 삼성전자에 요청에 의해 만들어진 기업인가요?

- 그렇지는 않고요. 미래의 성장성을 보고 투자하고 있다고 보시면 됩니다.

2. PLP공정을 하기 위해서는 새로운 장비 개발과 재료 간의 열팽창 계수의 차이로 휨 현상 발생등의 해결해야 할 요소가 있는 것으로 알고 있습니다. 이 부분은 어떻게 해결해 나가고 있나요?

- 이미 해결해서 양산중에 있습니다.

3. 패키징공정에 있어 PLP공정의 확장성이 기업의 성장과 밀접한 연관이 있어 보입니다. 관련 기술의 확장성에 대해 말씀해 주실 수 있을까요?

- 일반적으로 반도체의 성장이 연간 3~5%라고 봤을 때, FOPLP는 4배 정도 성장할 것이라 보고 있습니다.

3. 네패스라웨의 종속회사 네패스하임의 사업영역은 어떻게 되나요?

- FOPLP 비즈니스를 합니다.

3-1. 그렇다면 라웨와 하임의 차이는 무엇일까요?

- 라웨는 스퀘어 타입으로 양산을 하고 하임은 라운드 타입으로 하고 필리핀에 위치하고 있습니다.

4. 네패스아크의 CIS 테스트는 언제 시작될 계획인가요?

- 당장은 생산하고 있는 애플리케이션을 대응하는 것이 먼저이고 2~3년 정도 틈이 있습니다.

5. 네패스 아크의 신설공장이 21년~22년 공사로 되어 있는데 완공되었습니까? 언론 내용을 보면 995억 원이고 공시에는 631억 원 시설투자 중으로 차이가 있습니다. 어느 것이 맞는 것인가요?

- 공시 내용이 맞습니다. 아시는 바와 같이 지금 반도체 업황이 좋지 않아 서두르지는 않고 있습니다. 23년 2분기부터 설비 이동이 될 것으로 보입니다.

5-1. 거래 상대방은 미국의 반도체 테스트 장비 공급사 Teradyne(테라다인) 외 4개 회사로 SoC과 AP관련 설비라는데 맞습니까?

- 그렇죠 그런데 어떤 장비를 세팅하느냐에 따라 달라지는 것이죠. 저의 메인 제품 중에 어느 것을 세팅하느냐에 따라 달라지는 겁니다.

5-2. 이번 네패스아크의 신설 CAPA의 증설로 어느 정도의 매출 향상을 기대하시나요?

- 글쎄요, 디자인 CAPA로는 현재 매출 대비 3~4배로 예상됩니다.(22년 3분기 기준 네패스아크 매출 1,176억)

8. 투자 관점

네패스는 국내 3대 패키징 업체 중 유일하게 high-end급 패키징만을 하는 기업으로 앞으로의 성장성을 주목해봐야 합니다. 특히, 국내 유일의 FOPLP관련 기업으로 삼성전자의 반도체 성장과 상생하여 FOPLP 분야에 대한 성장이 기대됩니다.

'반도체, 삼성전자' 카테고리의 다른 글

| AI(Artificial Intelligence)의 과거와 현재 그리고 Processor (CPU, GPU, NPU, Neuromorphic Chip)와 삼성전자(반도체), (2) | 2023.08.23 |

|---|---|

| [기업분석]대한 민국의 미래를 이끌어갈 IP기업, 한국의 ARM "오픈엣지테크놀러지" (0) | 2023.07.08 |

| 흔들리는 TSMC의 파운드리 패권 (2) | 2023.02.22 |

| EUV Rinse 소재 국산화 성공한 영창케미칼(관련 소재 공부 이걸로 완전 정복) (2) | 2023.02.12 |

| 반도체의 미래 EUV PR 국산화 성공 동진쎄미켐 이걸로 끝~! (0) | 2023.02.09 |

댓글